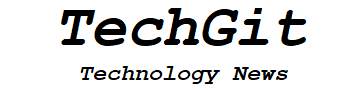

In what seems to be a major blunder by the SiPearl PR team, a recent visit by a local French politician resulted in the public Twitter posting in what looks like the floor plan of the company’s first-generation server chip project “Rhea”.

During a visit of Alexandra Dublanche, a local Île-de-France politician and vice president of economic development and other responsibilities for the region, the PR teams had made some photo-op captures of a tour of the office. Amongst the published pictures includes a shot of the company’s Rhea server chip project with some new, until now unreleased details of the European Processor Initiative-backed project.

In a close-up and up-scaling of the image, we can see that it’s a detailed floor-plan of the server SoC Rhea, labelled for a target TSMC 7nm process.

We can detail 72 CPU cores and 68 mesh network L3 cache slices in the floor plan, surrounded by various IP whose labels are too small to be legible. SiPearl had previously confirmed that the project uses Arm’s upcoming Neoverse “Zeus” cores which succeed the Neoverse N1 Ares cores that are being used in current generation Arm server SoC designs such as Amazon’s Graviton2 or Ampere’s Altra.

Beyond the confirmation of a core-count, we also see that the Rhea design sports a high-end memory subsystem, with the floor plan labelled as having 4x HBM2E controllers and 4-6 DDR5 controllers. Such a hybrid memory system would allow for extremely high bandwidth to be able to feed such a large number of cores, while still falling back to regular DIMMs to be able to scale in memory capacity.

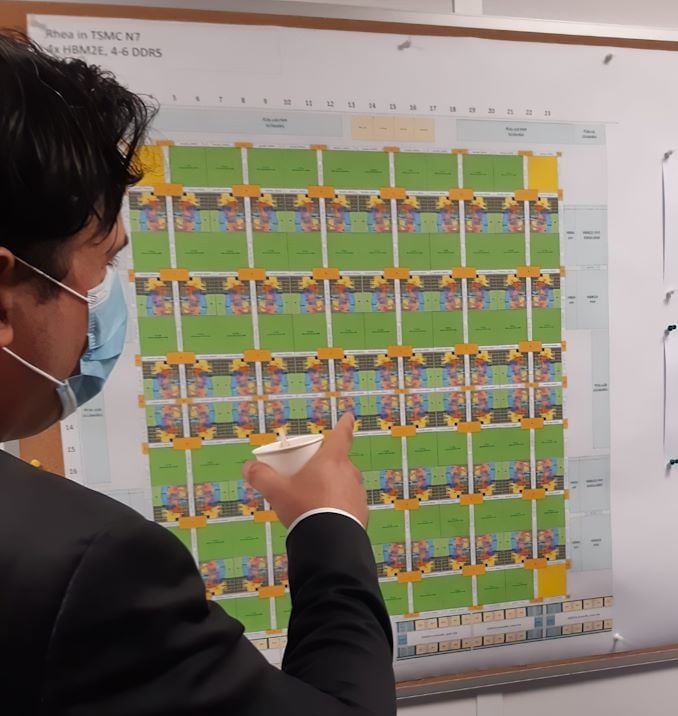

The Rhea family of processors is roadmapped to come to market in 2021. The only curious divergence here is that SiPearl previously stated that this was an N6 project, whilst the recent Twitter picture states it being N7. Given that both processes are design compatible, it might just be a recent shift in the project, or the company still plans to productise it in the N6 node when it comes to market.

The design’s aggressive memory subsystem with the inclusion of HBM2E points out that the company is aiming for quite high performance targets, joining the ranks of Fujitsu in terms of designing a CPU with advanced HBM memory.